BNN

Binäre Neuronale Netze für Mehrlevel-Umrichter

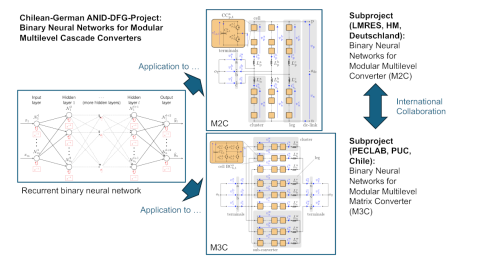

In diesem Projekt sollen weltweit zum ersten Mal binäre neuronale Netze in der Leistungselektronik eingesetzt werden, um Performanz und Zuverlässigkeit komplexer Umrichtertopologien zu steigern.

Es sollen binäre neuronale Netze (BNN) zum ersten Mal für Mehrlevel-Umrichter eingesetzt werden, um deren Potential in den Bereichen Modulationsverfahren, Beobachterentwurf, Fehlerdetektion & -diagnose (FDD) und fehlertolerante Regelung von leistungselektronischen Systemen zu untersuchen. Hierdurch sollen folgende Forschungsfragen beantwortet werden:

- Ist eine Implementierung von BNNs auf FPGA-basierten Realzeit-Systemen von Mehrlevel-Umrichtern machbar?

- Ist die Anwendung von BNN in den Bereichen Modulation, Beobachterentwurf, Fehlerdetektion & -diagnose und fehlertoleranter Regelung von Mehrlevel-Umrichtern zielführend?

- Ist eine signifikante Verbesserung der Performanz von Mehrlevel-Umrichtern mithilfe von BNN-basierten Modulationsverfahren, Beobachterimplementierungen, FDD und fehlertoleranten Regelverfahren zu erreichen?

Das chilenisch-deutsche Forschungsprojekt wird vom Labor für mechatronische und regenerative Energiesysteme (LMRES) an der Hochschule München, Deutschland und dem Power Energy Conversion Laboratory (PECLAB), Pontifical Catholic University of Chile, Chile durchgeführt. Die enge Zusammenarbeit der beiden Labore soll Antworten auf obige Fragen für die am häufigsten eingesetzten Mehrlevel-Umrichter-Topologien - der Dual-Star Chopper Cell Modular Multilevel Cascade Converters (DSCC-MMCC) und der Triple-Star Bridge Cell Modular Multilevel Cascade Converters (TSBC-MMCC) - geben. Der Fokus des LMRES liegt hierbei auf dem DSCC-MMCC, während das PECLAB vorrangig den TSBC-MMCC untersuchen wird.

Projektmitarbeitende:

- Jhonattan Berger-Diaz

Allgemeine Informationen zum Projekt:

- Laufzeit: 01.05.2024 - 01.02.2027

- Zuwendungsgeber: Deutsche Forschungsgemeinschaft (DFG)

Projektpartner:

- Pontifical Catholic University of Chile (Power Energy Conversion Laboratory (PECLAB))